Nachdem die ersten drei Projekte sehr ausführlich besprochen wurden,

wird ab diesem Projekt nur noch über das VHDL-Program und den

Pin-Planer gesprochen. Was hier neu ist, dass man ein Projekt

nicht komplett in einem Programm erstellt, sondern einzelne Module

programmiert und diese dann am Ende zu dem Projekt zusammenfasst.

Bei den Attiny- bzw Atmega-Projekten wurde der Timer eingeführt. Ein

Timer dient dazu aus dem Systemtakt, der für viele Anwendungen zu

schnell ist, laängere Zeiten zu generieren. Bei 50 MHz Systemtakt liegt

zwischen zwei Taktzeiten gerade mal 20ns. Während bei den Attinys und

den Atmegas die Bitbreite der Time mit 8bit und 16bit fest vorgegeben

war, können wir vom Prinzip her beliebige Bitbreiten verwenden.

Bei einem Timer wird ein Startwert bei jedem Systemtakt

heruntergezählt. Erreicht der Timer den Wert '0', wird ein

Interrupt-Signal (auch Timerüberlauf genannt) auf '1' gesetzt und der

Timer wieder auf den Startwert gesetzt. Bei der nächsten Taktflanke

wird der Interrupt wieder auf '0' zurückgesetzt.

Timer

ohne Vorteiler

|

Um ein 1Hz-Signal zu erzeugen,

müssen wir den Systemtakt durch 50.000.000 teilen. Die nächste Zahl zur

Basis 2, die diesem Wert nahekommt ist 2 hoch 26 = 67.108.864, unser

Timer hätte also eine Bitbreite von 26 Bit.

|

Timer

mit Vorteiler

|

Um

Timer mit hoher Bitbreite zu

vermeiden, verwendet man bei Timern häufig einen Vorteiler. Dieser ist

immer eine Zahl zur Basis 2 (z.B. 8, 64, 256....). Solche Vorteiler

lassen sich aus dem anreihen T-Flipflops zusammensetzten. Verwenden wir

einen Vorteiler von 1024, so würde für unser Projekt ein 16bit-Timer

reichen. Allerdings erzeugen solche Timer dann einen Feler, wenn die

Anzahl der gezählten Takte keine ganze Zahl mehr ist. 50.000.000 kann

nur 7 mal durch 2 geteilt werden, danach erhält man keine ganze Zahl

mehr.

|

Aufgaben:

|

Ändere das

VHDL-Programm so um, dass du einen Timer mit 16bit benutzen kannst.

|

|

In Uhren sind

sogenannte Uhrenquarze verbaut. Diese haben eine Frequenz von 32,768

kHz. Warum ist diese Frequenz besonders geeignet um eine Uhr zu bauen?

|

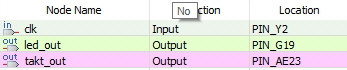

Ein einfacher Taktteiler für 1 Hz

Bevor wir an die Programmierung gehen, überlegen wir uns erst mal, wie

unser Projekt logisch aufgebaut sein soll und welche Ein- bzw. Ausgänge

benötigt werde. Der Systemtakt beträgt 50 MHz, dieser kann am Pin Y2

abgegriffen werden. Unseren Systemtakt nennen wir clk (für Clock). Um

zu überprüfen, ob unser Projekt auch das richtige tut, benutzen wir

neben einer Led (LEDR0 auf Pin G19) noch den SMA_CLKOUT Ausgang, dieser

ist auf Pin AE 23 zu geschaltet. Mit einem SMA zu BNC Adapter kann das

Ausgangssignal nun auf einen Oszillographen angezeigt werden.

Insgesamt haben wir also einen Eingang und 2 Ausgänge.

Systemtakt

clk

|

LEDR0

Led_out

|

SMA_CLKOUT

takt_out

|

PIN_Y2

|

PIN_G19

|

PIN_AE23

|

Für das Projekt werden zwei Module und die

Top-Level-Entity benötigt. In der

Top-Level-Entity

werden die Module zu unserem Projekt zusammengefügt, dort sind auch die

oben beschriebenen Ein- und Ausgänge definiert. Die Top-Level-Entity

bekommt den Namen

taktteiler_top.

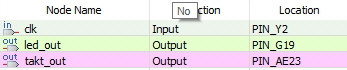

Der Pin-Planer sieht dann so aus:

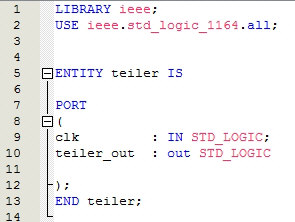

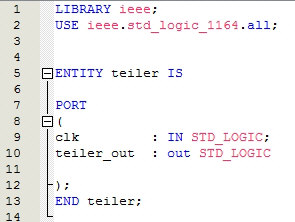

Das Modul Taktteiler

Module haben exakt den gleichen Aufbau wie unsere Projekte vorher,

allerdings werden die Ein- bzw. Ausgangssignale nicht nach außen

verbunden und tauchen damit auch nicht im Pin-Planer auf. Für unseren

Taktteiler benötigen wir einen Eingang

clk und einen Ausgang

teiler_out. Das Modul benennen wir mit

taktteiler.vhd

Das Programm selbst verwendet eine internes Signal

watch. Dieses

braucht nur die Werte von 0 bis 25.000.000 annehmen (da wir später das

Ausgangssignal in einem Flipflop speichern, dieses aber einen

Taktteiler um den Faktor 2 darstellt, müssen wir unseren Systemtakt nur

durch 25 Millionen teilen). Dieses Signal definieren wir mit

signal watch : integer range 0 to 25000000 := 0;

und weisen ihm direkt den Wert 0 zu (:=0).

Das Programm selbst ist sehr einfach gehalten. Erkennen wir eine steigende Taktflanke (

rising_edge) auf dem Eingabeport

clk so wird unser Signal

watch um eins nach oben gezählt. Erreichen wir den Wert 25 Millionen, so wird der Ausgang

teiler_out

auf '1' gelegt und das Signal wieder auf 0. Bei der nächsten Taktflanke

wechselt auch unser Ausgang wieder auf den Wert '0'. Wir erhalten damit

jeweils 10ns lange High-Signale, die sich alle 0,5s wiederholen. Das

Signal

watch hat hier also die Aufgabe einer Zählvariabel, so wie wir die z.B. aus JAVA kennen.

Damit ist unser Modul Taktteiler schon fertig.

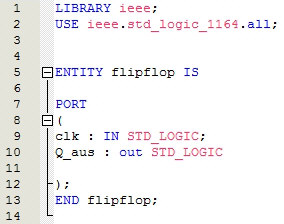

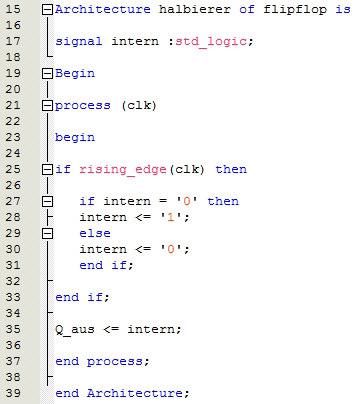

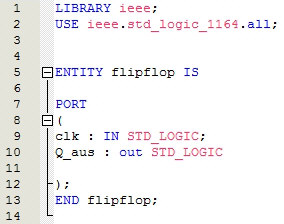

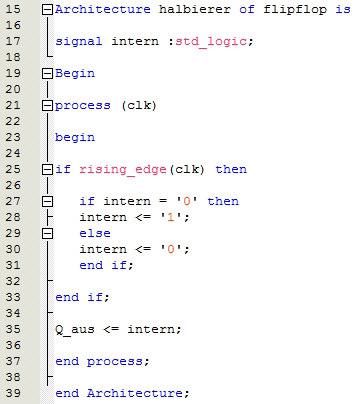

Das Modul Flipflop

Bei dem Modul Flipflop verwenden wir unser Takt-Flipflop aus dem

Projekt 3. Wir speichern es in einer neuen Datei, die wir flipflop.vhd

benennen.

Das Projekt Taktteiler - die Top-Level-Entity

Das Projekt Taktteiler - die Top-Level-Entity

Weiter oben wurde schon die Top-Level-Entity unseres Projektes

besprochen, nun müssen wir die einzelnen Module noch zusammenführen.

Dazu werden diese zuerst einmal in das Projekt eingebunden. Der Befehl

dazu lautet

component

gefolgt von dem Namen der Komponente und der ihr zugeordneten Ein- und

Ausgabeports. Der Name muss mit dem Namen in dem Modul übereinstimmen,

auch die Ports müssen richtig übernommen werden.

Für die Verbindung unserer Module brauchen wir noch zwei Signale, das Signal

aus und das Signal

intern. Die wir definieren müssen.

Das eigendliche Programm ist jetzt sehr schlank. Zuerst rufen wir das

Modul auf (der Name vor dem Doppelpunkt kann beliebig gewählt werde,.

nach dem Doppelpunkt steht der Name des Moduls der exakt sein muss.

Danach weisen wir die Signale zu. In der Top-level-Entity hat der

Systemtakt den Namen clk, den geben wir als Eingangssignal auf den

teiler, der teiler liefert uns ein Ausgangssignal zurück, welches wir

auf unser internes Signal intern geben.

Nun rufen wir unser Modul Flipflop auf. Diesem übergeben wir das Signal

intern als Eingabesignal und legen das Ausgabesignal von dem Flipflop auf unser internes Signal

aus.

Zum Schluß weisen wir unser internes Signal

aus unserer Led_out und dem Taktausgang takt_out zu.

Schauen wir uns das Signal nun mit einem Oszillographen an, so sehen wir schön das 1-Hz-Ausgangssignal.

Der große Vorteil der Module ist, dass wir ein sehr kurzes Programm

erhalten und dass wir die einzelnen Module vorher testen können. Die

Programmierung in Modulen ist also unbedingt empfehlenswert.

Das ganze Projekt kann als

Taktgeber.zip heruntergeladen werden.